# 特別企画 検出器シリーズ(12)

## 信号を処理する II (デジタル回路系)

田中真伸 高エネルギー加速器研究機構・素粒子原子核研究所

Email: manobu.tanaka@kek.jp

## 1. はじめに

放射光実験において、デジタル技術は検出器信号波形処 理、高速でインテリジェントなデータ収集、実験装置の一 部としてのビームラインの制御など、広い範囲で活用され るものです。では、検出器信号処理においてデジタル技術 はどのように使われているでしょうか? 前回のアナログ 回路系の記事で述べられているように, 検出器からの信号 を波形処理するためのデジタルフィルタはその具体例の一 つです。検出器信号処理におけるデジタル技術は実際に使 用されている個所は多いのですが、そのほとんどが産業技 術の転用であるため、ユーザーから見てブラックボックス 化しており、かつ産業/民生技術の進歩が速く技術の種類 も多岐にわたっているため全体を把握することが困難で す。そこで2章で具体的にマルチチャンネルアナライ ザーの例を示しながらデジタル技術の果たしている役割を 分類し、3章以降で検出器の信号をデジタル化するブロッ クである,アナログデジタル変換器 (ADC: Analog-to-Digital Converter) および時間デジタル変換器 (TDC: Time-to-Digital Converter) (3章), デジタル波形処理 (4 章), データ転送・収集(5章) について検出器からコン ピュータへのデジタルデータの流れに沿って説明していき ます。最後に、今後について議論します(6章)。

## 2. 検出器信号処理におけるデジタル技術

一般に人間が対象物を測定しその数値を定量化する場合,例えば物差しを見ながら大きさを測定する場合では,人によってばらつきはあるものの物差しの目盛の間隔以下

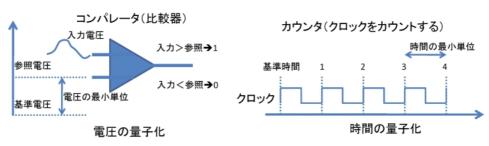

も読んで数値化します。これがアナログの世界の代表的な 測定手法です。一方、数値がデジタル化された場合は目盛 の間隔でしか値を表示しません(量子化)が、数値を客観 的にとらえることができます。このとき最小目盛り間隔を "1"としてその数値を2のべき乗で表記したものが2進 数です。一旦この表記を受け入れると全ての整数は"1" と"0"を使用し表示できます。この方法を検出器からの 電圧値の読み取りに使用した例がデジタル電圧メーターで あり、時間の表示に応用した例がデジタル時計です。Fig. 1に簡単な例を示します。デジタル回路では、例えば電圧 値を量子化する場合, コンパレータ (比較器) を使用しま す。これはアナログ回路系の記事で解説されたディスクリ ミネータと同じ機能で入力電圧を参照電圧と比較し大小の 判定を行い、その結果に応じて"0"や"1"に相当する電 圧を出力します。(この電圧値は信号の規格によって定義 が異なりその詳細は5章で紹介します。) コンパレータを 用い、かつ複数の参照電圧と入力を比較することで入力電 圧値は2進数を用い表すことができます。一方,時間に 関しては基準となるパルス間の時間間隔を持ったクロック と呼ばれるパルス列の信号を使用し、例えば一つのパルス が入ったら数字をひとつづつ加算していくといったように することで時間の量子化ができます。この時の時間の最小 単位はクロックのパルス幅とパルスの間隔の和です。この ような電圧の量子化と時間の量子化を同時に使用した技術 の例がアナログデジタル変換器(Analog-to-Digital Converter: ADC) で一定の時間間隔 (時間の量子化) で電圧 を複数の参照電圧と比較(電圧の量子化)を行いアナログ 波形をデジタル値に変換します。

このようにして数値を一旦量子化してしまえばデジタル

Fig. 1 量子化の例

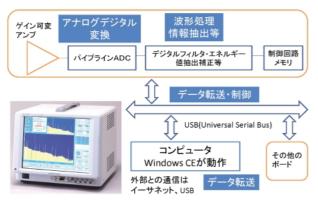

技術によってコンピュータまでデータを取り込み解析することが可能になります。この量子化以降の処理に関しては、マルチチャンネルアナライザー(MCA)を例にとり説明します。Fig. 2 はセイコー EG&G の MCA7600のブロックダイアグラムです。信号処理モジュールにおいて、アナログ回路(ゲイン可変アンプ)を通ってパイプラインADCと呼ばれるADCによってデジタル化された検出器信号は、デジタルシグナルプロセッサ(DSP)にて信号波形処理(デジタルフィルター)され、補正やエネルギー値を算出する等の情報抽出が行われ、それらのデータが記憶されます。この記憶されたデータに対するスペクトル表示、ウインドウを設定しスペクトルを積分する等の一連の解析操作は、MCA内のコンピュータモジュール(Windowsが動作している)によって制御されます。このMCAはユーザーの希望によってアナログ入力のチャンネ

Fig. 2 マルチチャンネルアナライザー MCA7600

ル数を増やすことや検出器用高圧発生モジュールをオプションで組み込むことができるようにしているため、コンピュータモジュールと信号処理モジュールは別々のモジュールとして製作され MCA 内で USB によって相互接続されています。また外部のコンピュータ等へデータを転送する場合はイーサネット等が使用できるようになっています。

この例でデジタル技術を使用している部分は青く囲ってありアンプ以外はほとんどデジタル技術であることが分かります。全体を通して信号の流れをみると、検出器からのアナログ信号は、まず(1)アナログ値をデジタル値に変換し、次に(2)波形処理・情報抽出等を行い、最後は(3)コンピュータへデータを転送するという手順に沿って処理されています。この処理の流れはどのような検出器を使用しても普遍的です。以降、この3つに分類した機能について、3章から5章にかけて詳細を記述します。

## 3. アナログ信号のデジタル化技術

アナログ信号をデジタル化(量子化)する部分、およびその逆の機能を持つ部分で、前述の ADC、TDC 等の要素がここに属します。ADC に関しては産業技術の進歩によるところが大きいため、動作原理とその動向を理解し、ADC の精度と変換速度の関係等を把握することは検出装置の性能改善にとって重要です。またチャンネル数が多い検出装置に関しては、ASIC(Application Specific Integrated Circuit:特定用途向け集積回路)や FPGA(Field Programmable Gate Array)等の技術を用いて小型化、高速化を行う必要があるため、ADC も含めこれらの技術が

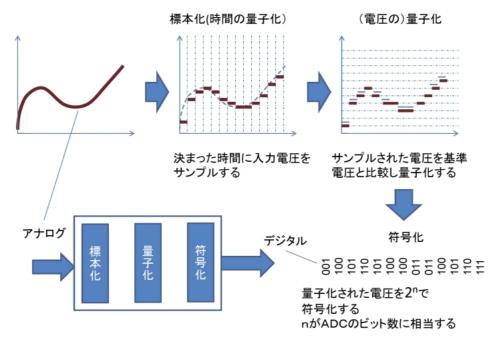

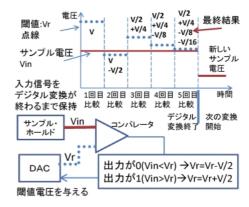

Fig. 3 アナログデジタル変換の概要

どういったものかを把握することは必要です。

#### 3.1 波形情報をデジタル化する

アナログ波形からエネルギー情報等を抽出する場合に使 用されるのが ADC です。Fig. 3 に ADC の動作概念図を示 します。ADC はまず入力のアナログ電圧を決まった時間 にサンプリングし (標本化:時間軸の量子化), そのサン プリングした電圧をコンパレータ(比較器:ディスクリミ ネ―タということもある)で複数の基準電圧と比較し決ま った精度で値を表します(量子化)。アナログ信号を忠実 に再現するデジタルデータを得ようと思えば高速の標本化 と高精度の量子化が重要ですが、一般に変換速度を上げる と精度が落ちるという相関関係があります。この相関は データ処理の観点からは注意すべきことで、消費電力・チ ャンネル数・データ転送時間・解析時間等の最適化を行う ために,アナログ技術による情報抽出とデジタル技術によ る情報抽出を併用する必要があります。このため複数のア ナログデジタル変換方式が目的に応じて使用されていま す1)。

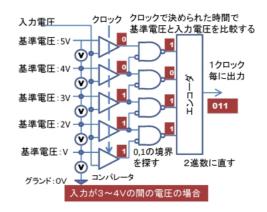

Fig. 4 と Fig. 5 に特徴的な 2 つの ADC の動作原理を示し ます。Fig. 4 はフラッシュ ADC の例で、アナログデータ をサンプリングするタイミングはクロックできまり、その クロックの入った瞬間にコンパレータが動作し量子化の電 圧 V で決められた量子化出力が得られます。Fig. 5 の上段 に5ビット逐次比較 ADC の動作,下段にブロック図を示 します。入力のアナログ信号は一旦サンプルホールドと呼 ばれる回路で保持され、その値と閾値が比較され1回目 の比較が終了します。この比較をコンパレータの出力を見 ながら閾値を変化させ比較することでアナログ値を量子化 していきます。この2つの例を比較すればわかるよう に、動作が速いことは標本化・量子化を少数回で行うこと を意味し,精度を上げることは多くの比較を同時に,もし くは別々の時間に行うことを意味します。よって12ビッ トのフラッシュ ADC の場合,動作を1回で終了させるた めサンプリング及び比較するための回路が1024個は必要

であり高速ながら消費電力が多くまた回路規模も大きくなることがわかります。また、逐次比較 ADC の場合はコンパレータ等の回路規模が小さく、一つでいいが精度を上げるためには多数回標本化・量子化をしなくてはいけないことがわかります。よって前述のように一般的には変換速度と精度の間には負の相関があります。

#### 3.2 パルスの到達時間を測定する

時間情報を抽出する場合に使用される回路を Time-to-

Fig. 4 FlashADC の原理

Fig. 5 逐次比較 ADC の原理

Fig. 6 TDC の動作原理図

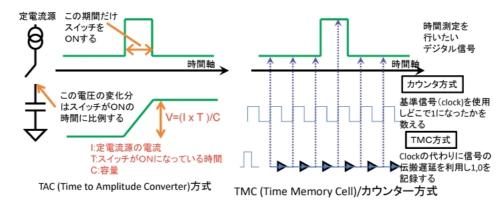

Digital Converter: TDC と呼びます。**Fig. 6**に動作原理の 例を示します。Fig. 6 左は TAC (Time-to-Amplitude Converter) 方式と呼ばれているもので、定電流源(一定の電 流を流すもの)とスイッチから構成されます。測定したい 時間の間一定の電流をコンデンサーへ流し込むことで、電 流がコンデンサにより積分されるためその時間間隔に比例 した電圧を出力する方法です。もうひとつは Fig. 6 右に示 されているようにデジタルパルスの形状をデジタル信号で 直接記録するものです。これには基準信号(クロック)を 使用する方法(カウンター方式)と遅延回路を使用して短 い時間間隔を作り出しそれによって記録する方法(タイム メモリーセル方式)の2つがあり、これらの複数の方法 を併用しているものもあります。TDCは、例えば試料に 外乱を与えた後もしくは反応を起こさせた後の試料の変化 をみる場合に使用されます。現在我々が使用可能な TDC の測定可能な時間精度は数十 psec が最小です。高時間分 解能の TDC を用いることで高速不可逆変化の記録や,可 逆であっても一気に全てのデータを記録することで測定時 間を短縮することが可能となります。

## 4. 信号のデジタル処理とその高速化

通常であればこうして得たデジタルデータをコンピュータへ転送し、ソフトウエアによってデータ解析を行いますが、次のような場合ハードウエアによるデジタル信号処理が必要になってきます。

(i)複雑な信号処理を高速に行い S/N 比をあげる必要がある。(ii)多量のデータを収集するためデータ抽出及び圧縮を行い記録媒体へデータを転送する。例えば放射光強度の増加、検出器チャンネル数の増加に対応するためやコンビ

ナトリアル手法による多量の試料試験を行う場合。(ii)多結 晶試料に対するビーム位置等の制御などです。今後,放射 光の輝度が上がるにつれ膨大なデータが瞬時に蓄積される ため高速で解析処理すること,及び積極的にデータ量を減 らす手法(データ圧縮)が必要になると予想されます。

これらを実現するための要素技術としてはデジタルシグナルプロセッサ(DSP)フィールドプログラマブルゲートアレー(FPGA)が存在します。DSPとは信号処理向けに特化した機能を持つ演算処理回路でC言語等のプログラムにより必要な機能を実現します。FPGAはDSPと異なりAND,OR等のプリミティブな要素の接続を直接プログラム(ファームウエアと呼びます)によって記述するものです。技術の詳細は参考文献を参照していただければと思います。ここではFPGAを例にとりこれらの要素技術がどのように役立つのかを実際の例を見ていただくことでその効果と重要性を理解していただければと思います。

## 4.1 FPGA を用いたデジタルシグナルプロセッシング

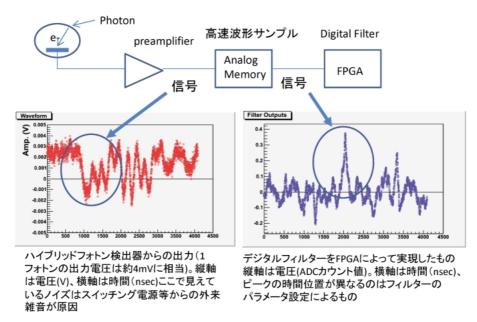

Fig. 7 はハイブリッド光センサーの信号処理例です。この信号処理系では微弱光信号をプリアンプで電荷電圧変換したのちに1 GHz の速度で電圧波形を記録し(Analog-Memory と書いてある部分),FPGA 内でデジタルフィルターをかけ信号対ノイズ比を上げています<sup>2)</sup>。この測定環境ではS/N比(信号対ノイズ比)が平均5以下で普通のローパスフィルターでは信号検出が困難です。Fig. 7 左はプリアンプの出力で,これをFPGAでデジタルフィルタリングした結果がFig. 7 右になります。このフィルタで行っていることは,信号のない場合のノイズを周波数空間で記憶しておいて,シグナル対ノイズ比が最大になるように各周波数成分に重みをつけることです。その結果としてこ

Fig. 7 デジタルフィルターの効果の例

Fig. 8 データ抽出・圧縮の例

の測定環境下でも、このフィルターを使用することで、エネルギー分解能は1光子を区別可能にし、且つ時間分解能も100 psec 未満の性能を出せています。これに似たフィルタ(カスプ型)はアナログ回路でも実装することができますが³)、多チャンネル化及び性能の安定性を考えると製作が大変なうえに、FPGAで行うような"環境が変わってもS/N比を最大にできる"柔軟性を持たせることは困難です。その点でデジタル技術がアナログ技術を補完しシステムの性能を最大限に引き出す柔軟性を付け加えているよい例です。

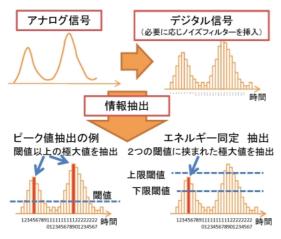

## 4.2 データ圧縮

デジタル波形処理を行い S/N 比を上げただけでは、波 形情報をそのままコンピュータへ転送しなくてはならない ため必要以上にバンド幅の広い転送システムが必要となり ます。しかしながら我々が必要な情報はエネルギー値等の 情報であり、それはすでに議論のあった情報抽出を行うこ とで、データ量を圧縮できます。Fig. 8 の左は一番簡単な 例で, ある閾値以上のデータの中で入力波高値のピークの 値とその記録された時間を検出するものです。また測定し たいエネルギー範囲が決まっている場合は右のようにエネ ルギー幅を指定し同様のことを行うことも容易にできま す。更にこのままではデジタル化された時の誤差が残るた め、場合によっては波形のピーク値周りの情報をピーク値 も含め数点抽出し、関数フィットすることで更に正確なエ ネルギーと時間を抽出することもできます。ここで強調す べきことは、閾値を変更する、極大値を抽出する、極大値 周りのデジタル信号も抽出する等の操作は FPGA 等によ って実現しやすいため、デジタル技術を信号処理に取り込 むことができれば、実験条件及び試料の変更を行いながら データを取るような多次元多変量空間での実験を行いやす いという利点を持つことです。

更にこのような実際の物理量を抽出する処理機能以外の 例として X 線回折パターンに関する応用があります。近

Fig. 9 MATLAB を使用したデジタルフィルター設計の例

年可逆データ圧縮の技術も進歩しており JPEG2000等の規格が制定され規格に準拠した専用集積回路等も売り出されています。画像圧縮技術を使うと2次元ピクセル検出器の画像圧縮が可能となるため、今後このような可逆変換画像圧縮を高輝度放射光実験に積極的に取り入れピクセル検出器のデータ量を減らすことが重要となっていきます。

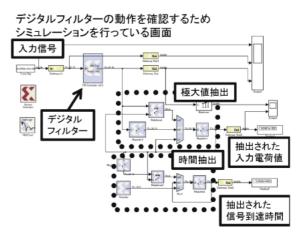

#### 4.3 デジタル処理用ツール

ここまで、この FPGA・DSP を使用しデザインをどの ように行うかに関しては触れていませんでした。DSP に 関してはソフトウエア (解析プログラム等) を書いたこと がある方であれば、敷居が低いと思いますので、FPGA に関しての例を示したいと思います。ここでは FPGA を 設計するためのツールとして MATLAB を挙げておきま す。FPGA は通常 HDL (Hardware Discription Language) と呼ばれる言語によって回路の記述を行います。 現在よく使用されている HDL は Verilog-HDL と VHDL の2種類ですが、初心者にとっては敷居が高くデザイン に時間がかかります。MATLABを使用した場合、Fig. 9 のように機能ブロックを配置・配線することで高機能モジ ュールを作り上げることができるため便利です。この例で は入力信号をデジタルフィルターに入れ波高値とその時間 を抽出し出力する機能を持つ FPGA をデザインし、実際 のデータを使用しながらデザインの検証を行っているとこ ろです。デジタルフィルターなどは HDL でも記述できま すが、MATLABではフィルターの特性を決める幾つかの パラメータをインタラクティブにフィルターブロックに記 入することで容易に機能を実現します。また実際のデータ 等をテストデータとして入力しシミュレーションを行うた めの機能ブロックも用意されており、HDL 等が使用でき ない人でもデザインを行うことができます。通常はこのよ うに用意されているモジュールを視覚的に接続し必要な機 能を作り上げることで生産性を上げつつ、慣れてくれば HDL を使用しながら製作することを行います。このよう

なツールは DSP デザイン用にも提供されています。

## 5. データの収集・転送について

データ収集速度の高速化は放射光の高輝度化に伴い重要になってきており、データ転送・収集の方法を検討することによってデータ取得速度を向上させることができるなら、必要なデータを効率よく短時間で収集できます。コンピュータがデータを収集するには、デジタルデータ送信側がコンピュータに理解できる言葉を話す必要があります。これを規格と呼び、そこでは電気特性、機械特性等が定義されています。電気特性に関しては音声の周波数に対応する"信号のレベル"と言語の文法に対応する"信号のタイミング"について主に定義されており、機械的特性についてはモジュールの大きさ、そのモジュールを格納するための筐体の仕様、コネクタの信号の配置等が定義されています。

#### 5.1 規格の変遷

データを収集・転送する場合に信号線を多数本使用するか、そうでないかによって規格を分類するとパラレル転送方式とシリアル転送方式に分けることができます(現実ではこの中間の特性をもったものも存在し、その境界はあいまいです)。また信号転送線を複数のモジュールで共有しているものをバスと呼びます。我々になじみのあるパラレルバス規格としては CAMAC (Computer Automated Measurement And Control)、VME (VERSAmodule Eurocard)、PCI (Peripheral Component Interconnect)等があります。

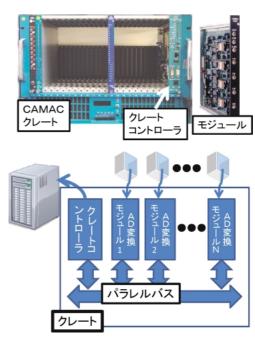

このうち一番古く規格化されたものは CAMAC です。 Fig. 10 に CAMAC モジュール、およびクレートを示します。この時代にはコンピュータは PDP11等の高価なものしかなく一台のコンピュータで多くの機器を制御、データ収集できるようなパラレルバス構造をもったものが使用されました。この傾向は現在の安価なパーソナルコンピュー

タ(PC)が登場されるまで続き VME 規格は産業用途として主にファクトリーオートメーション関連(工場での生産ラインの制御・データ処理等)で広まりました。このパラレルバス接続はデータ転送速度が速い等の利点がありますが、モジュール間を接続すべき信号線の本数が多く、離れた複数のモジュール・クレートを接続するのに不向きです。それに対し信号線の本数が少ないバス規格として存在するものが GPIB, USB (Universal Serial Bus) Ethernet: TCP/IPです。またバスではありませんが RS232C はシリアル信号線でデータを転送するための規格で、その簡単さから現在でも制御関係の信号転送規格としてよく使用されています。シリアル転送方式は信号線の本数が少ないため信号転送速度は遅く、以前はデータ転送にはあまり使用されてきませんでした。しかしながら近年デジタル技術が発達し数百メガビット/秒 (Mbps) を超える転送速度を

Fig. 10 パラレルバス接続 CAMAC の例

| Tahla 1  | 高速シリアルデータ転送り   | 日相枚乃び | RS232C  | CPIR |

|----------|----------------|-------|---------|------|

| I ADIC I | - 向坯ンリノルナーグ転坯/ | †別俗及し | K3232C, | GLID |

| 規格             | 速度(bit/sec)                    | 用途,特徵                             |

|----------------|--------------------------------|-----------------------------------|

| RS232C         | 115.2 k(ただし環境に依存する)            | 電源、モニター、モデム等とコンピュータの通信用途          |

| GPIB (IEEE488) | 8 M (64 M : Max)               | 計測機器の制御・データ転送で使用が多い。総ケーブル長20 m    |

| イーサネット         | 10 M, 100 M, 1 G, 10 G (100 G) | 産業用途,民生用途<br>長距離通信可               |

| USB            | 12 M, 480 M, 5 G               | 民生用途 (コンピュータと周辺機器) 短離 (数 m)       |

| Infiniband     | 2 G                            | 民生用途(コンピュータサーバー用インターコネクト)低レイテンシ   |

| ファイバーチャンネル     | 1 G, 2 G, 4 G, 8 G (10 G)      | 民生用途 (ハードディスク等のストレージデバイス用)        |

| PCI Express    | 5 G                            | 民生用途(コンピュータボード内バス、通信用ボード内等で使用される) |

民生用途:コンピュータ,通信等 産業用途:民生用途以外にファクトリーオートメーション等を含む

持つ規格が使用可能になっており、これによって多くのと ころで USB, イーサネット等が使用されるようになりま した<sup>4)</sup>。**Table 1**に,なじみのある規格(RS232C, GPIB) と高速データ転送用に使用される規格をまとめておきま す。イーサネット (TCP/IP) 以外は主にコンピュータ同 士もしくはコンピュータの外部機器との接続に使用される ことが多く、規格としてもコンピュータの進歩に伴い変遷 を繰り返しており他にも多数存在します。このような高速 シリアル転送技術の発展を背景にデータ転送・収集の方式 も変化しつつあります。例えば Fig. 10 で示したパラレル バス接続から Fig. 11 に示すように、検出器をセグメント化 しモジュール間をシリアルバス等で接続, データを収集・ 転送することが多くなっています。言い変えると,パラレ ルバス方式でのクレート・モジュール類を細かく分割した うえで、それぞれを一枚のボードにしてしまい、そのボー ドとコンピュータをシリアルバスで接続したと言えます。 これが可能になった背景には、集積回路技術の進歩による モジュール類の小型化、高機能化が存在します。この接続 方法の最大の利点は、接続線を増やすことでシステム全体

Fig. 11 シリアル接続 ネットワークの例

の転送速度を増加させやすい(スケーラブルなシステムであるという)ことです。これらの技術のおかげで2次元イメージング検出器に代表される多チャンネル検出器を多く使用し高速にデータ転送・解析することが可能になってきています。

#### 5.2 高速化・分散化 (多チャンネル化)

システム全体のデータ収集速度を向上させることは高輝度放射光実験において必須です。処方箋はデータ量そのものを減らすこと、データ転送速度を増加させることの2つがあります。ここではまずデータ転送の不感時間についての簡単な考察を行った後、データ転送速度を向上させるための幾つかの技術について具体例をあげ解説します。

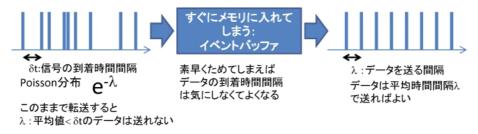

## イベントバッファによるデータ到着送信間隔の平滑化

自然現象はランダムに起こるので検出器から受け取る信号の時間間隔はポアッソン分布に従います。よってデータ転送速度がこのデータ到着の平均時間間隔と同じであってもデータ損失がおきます(検出器の不感時間と同じ考え方です)。この場合には一度データをためる場所(以降イベントバッファと呼ぶ)を作ってあげれば、送信側の速度は平均値のままで取りこぼしがなくなります(Fig. 12 参照)。

## デジタル信号の規格と速度

すでに Table 1 において Ethernet, USB 等の規格を示しましたが、これらの規格は"物理的な電圧信号の規格"のみでなく"信号のやり取りの作法"も定義しています。実験を行う場合、これら以外に NIM, ECL 等も使用します。これらの規格は"物理的な電圧信号の規格"で"信号のやり取りの作法"は定義されていません。よく使用する信号の規格を Table 2 にまとめました。

既出の CAMAC・VME 規格は TTL/CMOS レベルを使用しており、USB、Ethernet 等は独自の規格を持っています。また近年、高速信号転送用に光信号が使用されるようになってきており直接 FPGA に接続し使用することが可能となってきました。このような光モジュールを使用することで高速データ転送が可能になるだけでなく、グランドループをなくし外来雑音を低減する等の利点もあります。

さて今後ますます FPGA 等,産業技術を多用する機会が増えてくるようになるため,NIM,ECL 等の負電源を

Fig. 12 イベントバッファの動作

| 電気信号規格                                               | ロジックレベル                                                                         | 特 徵                                                                 |

|------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------|

| ECL (Emitter Coupled Logic) PECL (Positive ECL)      | 600 mV<br>ECL: $-1.3 \pm 0.3$ V (typ)<br>PECL: Vcc-ECL                          | GHz 伝送可能<br>消費電力大・負電源必要<br>ケーブル転送可能<br>差動信号:100オームドライブ              |

| NIM                                                  | $0\sim-0.6 \text{ V(typ.)}$                                                     | 百 MHz 転送可能<br>NIM モジュールに使用・負電源必要<br>ケーブル転送可能<br>シングルエンド:50オーム       |

| TTL (Transister Transiser Logic)<br>CMOS Logic       | TTL: 0.8~2.0 V(typ.)<br>CMOS: 0.4 ~Vdd ~0.8 V(typ.)                             | 主にボード内信号転送に使用<br>高速信号を送るときは注意が必要<br>ケーブル転送には不向き<br>VME・CAMAC のバスで使用 |

| LVTTL (Low Voltage TTL)<br>LVCMOS (Low Voltage CMOS) | LVCMOS: 0~2.5 V                                                                 | TTL/CMOS と比べより速い信号を送りやすい。ケーブル転送には不向き<br>主にボード内において FPGA 入出力に使用      |

| LVDS (Low Voltage Differential Signaling)            | $\begin{array}{c} 300 \text{ mV} \\ 1.25 \pm 0.15 \text{ V (typ.)} \end{array}$ | 差動信号100オームドライブ<br>ケーブル転送可能<br>高速信号を送ることはできるがケーブル長に依存する。             |

Table 2 よく使用するデジタル信号規格

必要とする技術は特殊な用途(高速かつ特定のモジュール内の信号転送)でのみ使用されることになり、長期的にはモジュール間の信号転送は正電源のみを使用する信号規格が主流となる可能性が大きいでしょう。ただし現状では、資産・使いやすさ等の点からすぐにLVDSがNIM等に完全に置き換わることはないため、ECL/PECL/NIM信号を簡単にレベル変換できる集積回路を知っておくことは有用です。集積回路:SN65LVDS348は、入力のコモンモード範囲が広いためECL/NIM信号を受けてLVTTLに変換できます。この集積回路は入力信号がECL/NIMであっても負電源を使用せずにデジタル信号の受信ができFPGAに接続できるため便利です。

## データを転送する

データをコンピュータに転送する場合,実際は下記の点に気をつける必要があります。

(1) 規格で示されている速度は100%出せないという事 実。

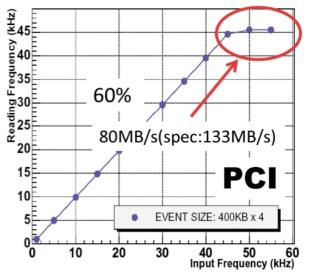

Fig. 13 を見てください。PCIの例です。規格では133 Mbyte/sec といわれていますが60%くらいの速度しか出ていません。原因は、コンピュータ内の中央演算処理集積回路(CPU)がデータ転送を始めるための初期化に時間がかかっていることです。使用しているハードウエア構成、オペレーティングシステムによって左右されるため初期化の時間は環境によって差がありますが、規格で決まっている速度を100%出すことは困難です。

(2) データ入出力インターフェースが標準のものである

この条件はコンピュータにデータを送るために必須です。これを満たす場合は高性能で安価なコンピュータが使用できますが、そうでない場合はコンピュータ間を接続するための独自規格のハードウエアを製作する必要があり、

Fig. 13 PCI 規格と実際のデータ転送速度

開発コスト,維持等の負担が増えます。パーソナルコンピュータでよく使用されているインターフェースとしては USB, イーサネット, PCI 等が挙げられます。

(3) 長期間使われていること(長持ちする技術であること)。

コンピュータ周りの技術の進歩は激しく、例えば前述のPCIバスは現在PCI-Express に置き換わりつつあります。このように技術の変化が激しいと、一度購入もしくは製作したデータ転送システムが短期間で使用不可能になります。我々が使用する加速器、測定システムの進歩速度に比べ民生産業機器の進歩、多様化は激しいため、安易な技術の選択はかえって負担を増やすことになります。この意味でインフラストラクチャとして広く使用されているイー

サネットはよい候補の1例です。

以降、ネットワークを例にとりその特質に触れたうえで どのように多量のデータを送ればいいかを議論していきま す。

#### 5.3 ネットワークでデータ収集を行うこと

一旦ネットワークを選んでしまえば、ネットワークはインフラストラクチャとして整備されているために多くの機器との接続が容易になり、かつ市販されている多くのツールが使用可能になります。ただし、検出器からのデータ転送にイーサネットを使用する場合は以下のような問題点を解決する必要があります。前述の PCI と同じ理由により規格の速度の100%を出すことは困難です。一方、データ転送速度を上げようとすると高速の CPU を使用せざるを得ないため大きさも消費電力も増え、1ギガビット/秒(Gbps)の速度を出せるような転送速度を持つ機能を個別の検出器につけることが困難になります。データが入ってから出るまでに遅延があり、その遅延が予測不可能であることも問題です。例えば複数のイメージング検出器からのイメージを統合して一つの大きなイメージを作り上げよう

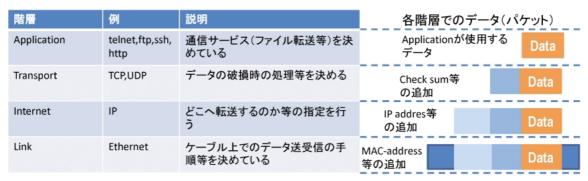

とした場合、検出器ごとに遅延に大きなばらつきがあると処理が複雑になったり、ネットワークを通じた制御が困難になります。これらの問題は CPU 及びソフトウエアに起因する問題です。通常、イーサネットを使用する場合、Fig. 14 の処理をコンピュータが行います。まず、データ収集ソフトウエアがデータを用意し(アプリケーション層)、通信規格に応じてデータの破損時の修復用のデータ等を追加し(トランスポート層)、どのコンピュータへ送るかを示す IP アドレスを追加し(インターネット層)、その他ハードウエアで決まったデータを追加し(リンク層)信号としてイーサネットへデータが送出されます。受け取る側も同様に送られてきたデータを読み込み IP アドレスを見て自分宛のものかそうでないかを判断し、自分宛のものであれば必要な処理をしたのちにデータを受け取り、そうでない場合はネットワーク上へデータを流します。

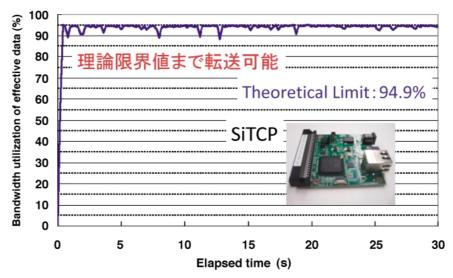

通常、アプリケーション層からインターネット層までのデータの処理は CPU によって行われるため前述のような問題点が起こります。しかしながらトランスポート層とインターネット層を FPGA 上に実装したもの(SiTCP)5)を使用した場合、Fig. 15 に示すように理論限界まで速度が出

Fig. 14 イーサネットの動作とデータを転送する場合の例

Fig. 15 イーサネットをハードウエア化した時の転送速度

るようになります。ここで縦軸はデータ転送を行った時の 転送速度で、横軸は転送を始めてからの時間です。また CPU を持たないため消費電力も非常に小さくなります。

このように一旦ハードウエア化できると,データ収集を イーサネットで行う方法では上記の問題点は解決され多く の利点をもたらします。

更に1本当たり1Gbpsのイーサネットを10本接続した場合は、検出システム全体として10Gbpsの速度を容易に出すことができます。前述のVME、CAMAC、PCIではモジュールの数を増やしてもバスの速度でシステム全体の速度が決まってしまうためこのようにネットワークの本数を増やしただけ速度が上がるということはありません。さらにネットワークスイッチ、コンピュータ等もインフラストラクチャとして整備されているためデータ転送システムを構築しやすいことは大きな利点です。これ以外にも現在発展しているWEB技術の導入が楽になりが、世の中に流通している多くのリソースを使用できるというソフトウエアの観点からの利点もあります。このように世の中の技術を実験にうまく取り込めるようになれば、同じ努力をしても得られる効果は全く異なり研究の速度も加速します。

## 6. 今後

さて、ここまで検出器からのデータ処理転送に関してアナログデジタル変換以降のシステムについて、デジタル技術がデータ処理・データ収集転送に役立っていることを見てきました。これらの技術が多量のデータを取り扱うための条件も明らかにし、その中でイーサネットを使用しデータ収集システムを構築すると世の中のインフラを広く使用できるようになるため有利であることも見てきました。

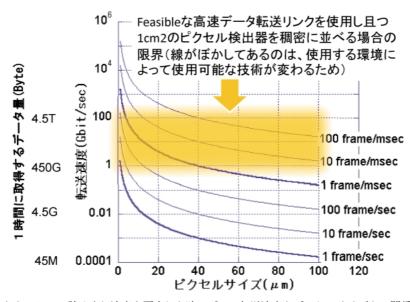

今後、放射光に限らず加速器のビーム強度はより強くな り、更にビームラインを含む測定システムは機能が向上 し、短時間で試料の特性を高精度に観測できるようになっ てきています。これらの動向はユーザーに利便性をもたら しますが、それと同時に短時間で大量のデータを取得・解 析する必要が出てきています。検出器システムを例にとれ ば、イメージング検出器はより高精細、ダイナミックレン ジはより大きく, 検出手法も時分割測定や試料の自動交 換、偏光度を短時間で変化させる等のビームライン及び試 料の自動交換等の制御が開始されており、以前より多くの データを素早く収集し記録媒体に書き込む必要が出てきて います。またこれらのデータが多量であれば多量であるほ ど解析時間が増大するため,記録媒体へ書き込む前に必要 なデータの取捨選択が必須となってきます。どのくらいの データを転送する必要があるかを,ピクセル検出器を例に とり Fig. 16 に示しました。

この図の横軸は検出器のピクセルサイズで、縦軸はデータ量を示します。各ピクセルが16ビットデータを読み出す時にどれくらいのデータ転送速度が必要となるか、が実線で書かれています。これを見れば時分割測定を行う場合にどれくらいのサイズの画像が読み出せるかがわかると思います。この図より画像を記録するには非常に多量のデータを読み出さなくてはならないということが分かっていただければと思います。では分光ではどうでしょうか。時間分解エネルギー分散 XAFS 法ではストリップ検出器を使用しており、例えば KEK の PF-AR リングのビームラインにおいて 1 usec おきに全てのデータを読みだそうとすると2000ストリップ×16 bit ×106 となり数 3 Gbps でデータを読み出す必要が出てきます。ここにあげた例は現時点ではデータを大量に転送する特別な実験ですが、このよう

**Fig. 16** 決められたフレーム読み出し速度を要求した時のデータ転送速度とピクセルサイズとの関係( $1 \, \mathrm{cm}^2$  のピクセル検出器を仮定)

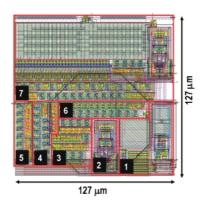

- 1. Opamp

- 2. Comparator

- 3. Ctrl. Logic

- 4. TOF counter

- 5. TOT counter

- 6. ADC register

- 7. SAR ADC

Fig. 17 高機能ピクセル検出器読み出し集積回路

な問題は高強度化を目指す放射光を有効に利用しようとすれば一般的に起こることと思います。こういった動向を踏まえたうえで検出器システム開発を見直してみた場合,検出器・アナログ技術・デジタル技術の融合を目指した開発は必然であると思われます。 $\mathbf{Fig.}$  17 は東京工業大学松澤研究室と KEK 測定器開発室 ASIC プロジェクトチーム(佐賀大学,京都大学等を含む)で開発しているピクセル検出器の1ピクセル分のレイアウト図です。

127 um 角のピクセル内にアナログ回路, ADC, TDC, メモリ, デジタル制御回路が組み込まれています。つまり, いままでの測定装置のうちほとんどの部分が1ピクセルに組み込まれています。今後このような技術が更に発展し検出器自身の高機能化が推進されれば, 高輝度放射光により高度で斬新な実験がおこなわれるようになり,この分野のアクティビティの向上が期待できます。

#### 斜辞

本稿における MCA7600の写真をセイコー・イージーアンドジー株式会社から提供していただきました。また執筆にあたり高エネルギー加速器研究機構 内田智久氏,東京大学 阿部俊範氏には資料を頂きました。ピクセル読み出し集積回路のレイアウト図を使用することに関し東京工業大学松澤昭氏,宮原正也氏に快諾していただきました。皆さまにお礼を申し上げます。

## 利用情報

- 1. デジタル回路そのものに関して "デジタル回路テイクオフ指南",小林芳直 CQ出版:初心者向け且つ実用的。

- 2. DSP に関して

http://ja.wikipedia.org/wiki/: デジタルシグナルプロセッサ: 概要のみ。

http://www.analog.com/jp/embedded-processing-dsp/processors/index.html: アナログデバイセズ社 DSP http://focus.tij.co.jp/jp/dsp/docs/dsphome.

tsp?sectionId=46:テキサスインスツルメンツ社 DSP

- 3. FPGA の導入等に関して

- http://japan.xilinx.com/: ザイリンクス社

- http://www.altera.co.jp/: アルテラ社

- http://japan.xilinx.com/support/training/

- free-courses.htm: ザイリンクス社の FPGA 入門

- 4. Hardware Description Language について

- "HDLによる高性能ディジタル回路設計",盛岡澄夫

- CQ 出版 ソフトウエア経験者用入門書。

- "RTL 設計スタイルガイド" VHDL 編, Verilog HDL 編 半導体理工学研究センター (実用的)

- 5. MATLAB について

- http://www.mathworks.co.jp/products/:制御関連・ デジタル信号処理・画像処理・実験計測

- 6. SiTCP について

- http://e-sys.kek.jp/tech/sitcp/: SiTCP のページ http://www.bbtech.co.jp/: SiTCP の評価キット購入 生

- 7. エレクトロニクス全般に関して

- "The Art of Electronics", Horowitz and Hill (アナログデジタル両方の概要,中級者向け)

- 8. パルスカウントタイプの検出器,実験に与えるノイズの影響

- "雜音",第4章 関英男 岩波全書

- 9. 放射線検出器用途集積回路及び FPGA に関して http://e-sys.kek.jp/seminar/2009/Advanced\_Seminar /:エレクトロニクスセミナー

http://e-sys.kek.jp/seminar/2009/ASIC/:集積回路 製作実習

http://e-sys.kek.jp/seminar/2009/FPGA/: FPGA セミナーのホームページ

10. 放射線計測用 CAMAC, VME モジュール等販売, 製

林栄精器㈱ http://www.repic.co.jp/

(前ジーエヌディー http://www.gn-d.com/

セイコー・イージーアンドジー(株)

http://speed.sii.co.jp/pub/segg/hp/index.jsp

㈱豊伸電子 http://www.kagaku.com/hoshin/

(制テクノエーピー http://www.techno-ap.com/

㈱ビー・ビーンズ・テクノロジーズ

http://www.bbtech.co.jp/

## 参考文献

- 1) 「CMOS アナログ回路設計技術」, トリケップス p. 93-129.

- 2) Y. Kawai et al.: Nucl. Instr. and Meth. A579, 42 (2007).

- V. Radeka: Ann Rev. Nucl. Part. Sci. Vol. 38, 217 (1988).

E. Gatti et al.: Nuovo Cimento 9, 84 (1986).

- 4) S. Satoh, et al.: Nucl. Instr. and Meth. A600, 103–106 (2009).

- T. Uchida: IEEE Trans. Nucl. Sci. 55, 1631 (2008).

- 6) T. Uchida et al.: IEEE Trans. Nucl. Sci. 56, 448 (2009).